# EGC442 Class Notes 4/28/2023

**Baback Izadi** Division of Engineering Programs bai@engr.newpaltz.edu

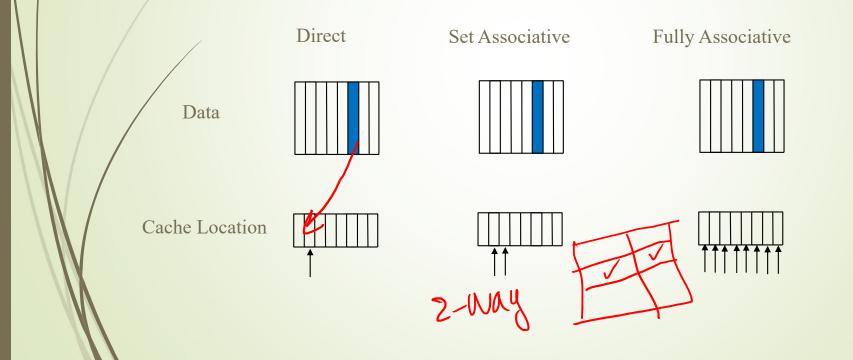

## Decreasing Miss Ratio with Associativity

Associativity: Reducing cache misses by more flexible placement of blocks

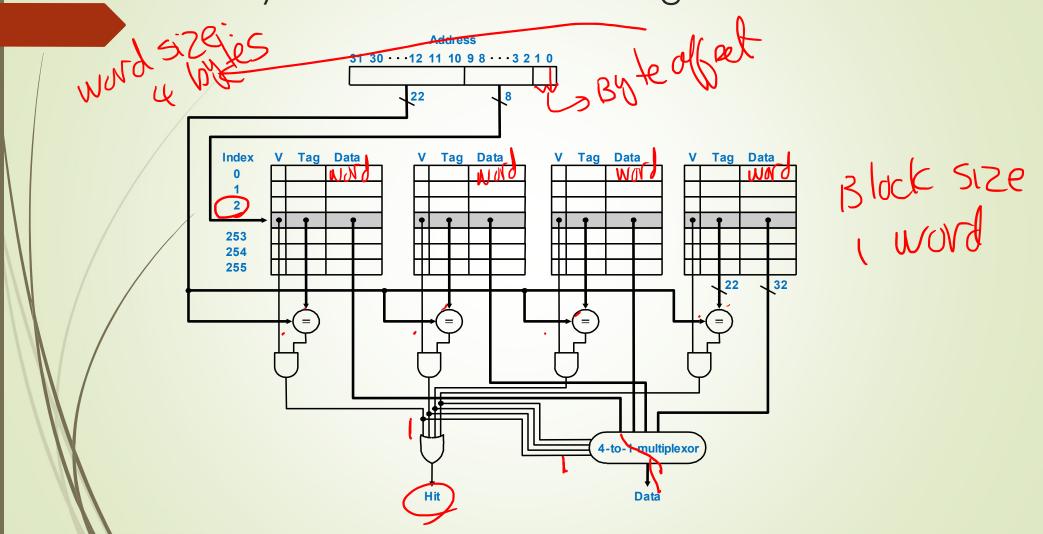

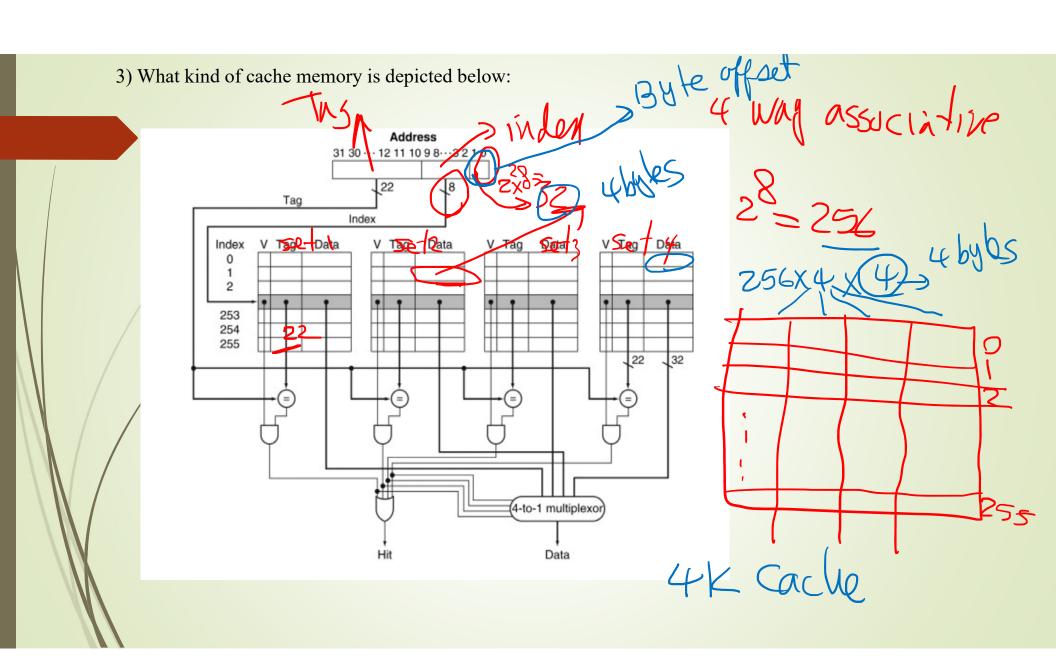

### 4-Way Associative Cache Organization

85

1) Assume a two-way set-associative cache with one byte word size, 8-one word blocks. Given the following sequence of block addresses, indicate if each request results in a cache hit or miss: 1, 9, 6, 5, 1, 6. Show the AIAU seti hits and misses and final cache contents. set 2

Miss

Miss

6 Miss

6

M135

POO

0 01 0 0

00

001

OOOO

0

) ()

00

5

word Sizk 2) Assume a fully associative cache with 4-one word blocks. Given the following sequence of block addresses, indicate if each request results in a cache hit or miss: 1, 9, 6, 5, 1, 6. Show the hits and misses and final cache contents. TIFIGISI II GH 7 Miss 7 Miss G Miss  $^{\prime}$ Miss Hit Miss Hit 6

The \_\_\_\_\_ of every cache block within the appropriate set of a setassociative cache is checked for a match against the memory block address.

- O index

- 🖲 tag

- O block offset

A four-way set-associative cache with 32-one word blocks requires \_\_\_\_\_ comparators to compare the tags of each element within the set.

- **()** 4

- O 8

- O 32

A direct mapped cache with 32-one word blocks requires \_\_\_\_\_ comparator(s) to compare the tags of of an element with the memory block address.

01

O 32

Which block in the cache is replaced by memory block 29?

Cache configuration: 4-way set-associative cache with 8-one word blocks

Replacement scheme: LRU

Sequence of previously accessed block addresses: 5, 13, 21, 13, 5 (Note: All memory block addresses map to cache set 1)

- O Mem[5]

- O Mem[13]

- O Mem[21]

- None. An element in set 1 is unused, so Mem[29] is placed in the fourth element of set 1.

#### Correct

The tags of all the blocks in the set must be searched to determine if the memory block is contained in the cache.

### Correct

4 indicates the numbers of blocks within a set and the number of comparators to determine which element of the selected set matches the tag.

#### Correct

A single comparator is needed because the entry can be in only one block of the cache.

16842 A4A3A2A1

5

13

29

Ø

#### Correct

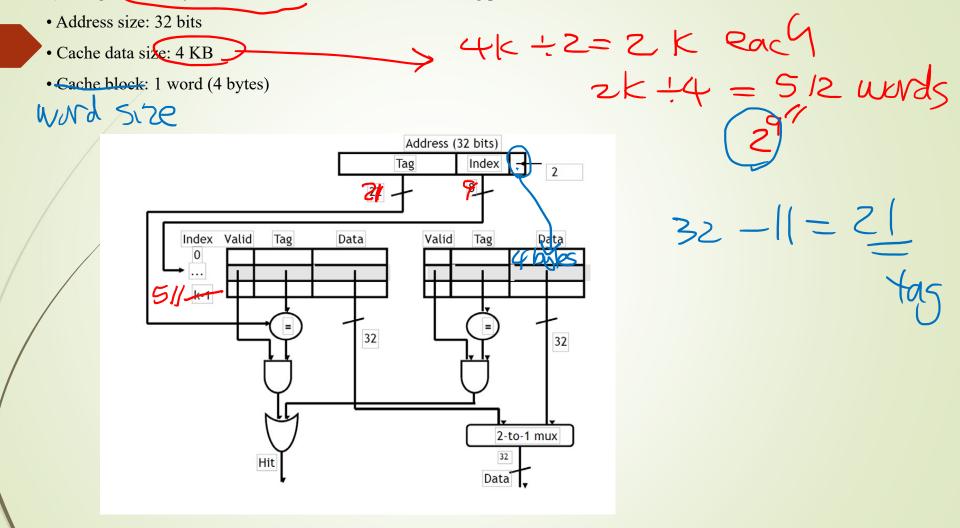

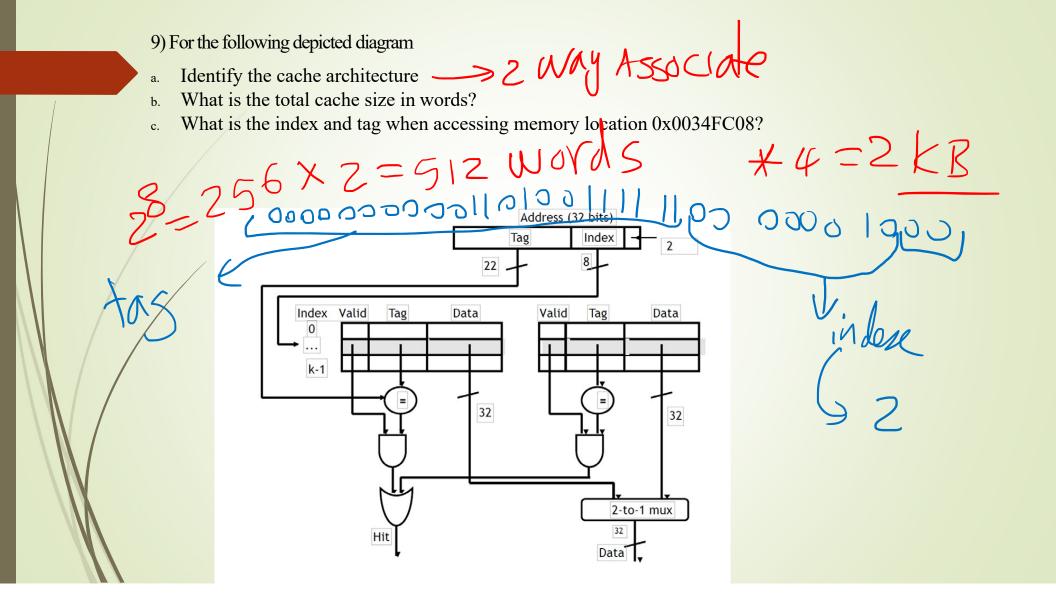

The cache has two sets (0 and 1) and 4 blocks per set. The fourth block of set 1 is unoccupied, thus Mem[29] is placed in the fourth block of set 1. The replacement scheme has not yet been used. 8) Design a two ways set associative cache with the following parameters:

> A2A A3

ZZ

| a.       | For two ways set as | sociative, show the hits and misses and  | final |

|----------|---------------------|------------------------------------------|-------|

|          |                     | 16 8 4 2 1<br>A4 A3A2 A, A0<br>O 1 0 0 1 | 4     |

| Location | Hit/Miss?           | 174 43+2 41170                           | G     |

| 9        | M                   |                                          | C     |

| 4        | $\sim$              | 00000                                    |       |

| 20       | $\square$           | 10100                                    |       |

| 4        | 424H                |                                          |       |

| 8        | M                   | 0 1 0 0 0                                |       |

| 15       |                     |                                          |       |

| 5        | N.                  |                                          |       |

| 19       | <u>N</u>            |                                          |       |

| 4        | H                   |                                          |       |

| 20       |                     |                                          |       |

| 4        |                     |                                          |       |

| 22       |                     |                                          |       |

| 7        |                     |                                          |       |

|          |                     |                                          |       |

b. For a fully associated cache, show the hits and misses and the final cache contents.

191420 815519271

| Location | Hit/Miss?     |

|----------|---------------|

| 9        | $\mathcal{M}$ |

| 4        |               |

| 20       | $\sim$        |

| 4        | H             |

| 8        | $\mathcal{M}$ |

| 15       | $\mathcal{M}$ |

| 5        | M             |

| 19       | $\mathcal{M}$ |

| 4        | H.            |

| 20       | H             |

| 4        | +             |

| 22       | M             |

| 7        |               |

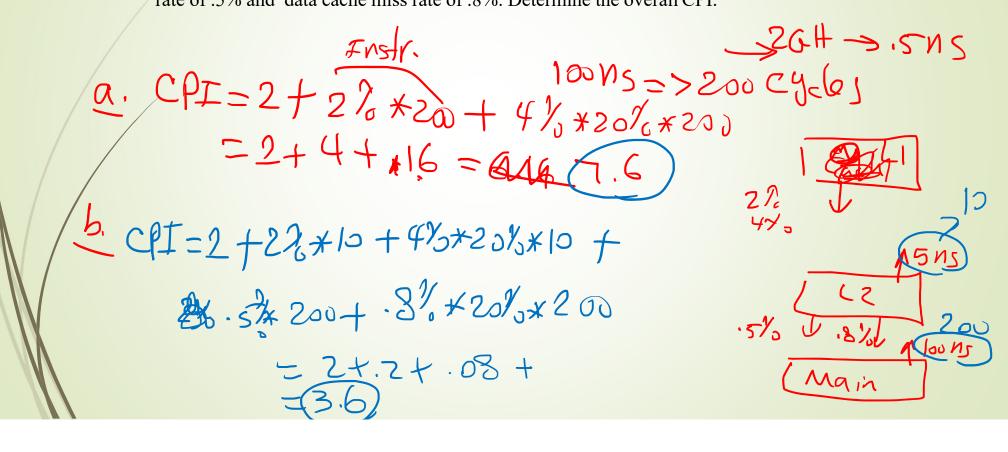

11. Assume an instruction cache miss rate for an application is 2% and the data cache miss rate of 4%. Assume further that our CPU is running at 2 GHz and has a CPI of 2 without any memory stalls. The main memory access time is 100 ns.

- a. Determine the overall CPI with the indicated misses, provided the frequency of all loads and stores in the application is 20%.

- Suppose we like to add a second level cache with an access time of 5 ns, which has an instruction miss rate of .5% and data cache miss rate of .8%. Determine the overall CPI.